Decoder

AIM: To develop HDL code for 2:4decoder.

Tools/Software

Required:

1.

Personal Computer.

2.

Vivado 2019.2 Software

3.

Verilog/VHDL

Theory: A decoder is a combinational logic circuit that has ‘n’

input signal lines and 2n output lines. In the 2:4 decoder, we have 2 input

lines and 4 output lines.

Procedure:

1.

Click on Vivado2017.2

icon.A window is opened.

2.

Click on File→New

Project→Press Next→Give

the Project name and Project Location→Press Next→Choose Project Type as RTL Project→Press

Next→

3.

Create File→File

Type: VHDL\VERILOG File Name→ Filename→Press Next→ Press Next→ Press Next→Finish.

4.

Write the module

definition by giving input ports and

output ports →Press Ok.

5.

Two workspaces are opened with names Project Manager and Flow Navigator

6.

In Project

Manager →Click on Sources →Design Sources→File→A window is opened with File

name. Write the Program in the File →Click on Save.

7.

In Flow

Navigator→Click on Simulation →Run Simulation→Run Behavioural Simulation→A window is

opened with name “untitled1”→Force Constants→Run

for 100 µs. Observe the simulation results for various combinations by

clicking on Zoom Out.

VHDL Code for 2 to 4 Decoder

library

IEEE;

use

IEEE.STD_LOGIC_1164.ALL;

entity

dec2to4 is

Port

( enable : in STD_LOGIC;

sw

: in STD_LOGIC_VECTOR (1 downto 0);

led

: out STD_LOGIC_VECTOR (3 downto 0));

end

dec2to4;

architecture

Behavioral of dec2to4 is

begin

led

<= "0000" when enable='0' else

"0001"

when sw="00" else

"0010"

when sw="01" else

"0100"

when sw="10" else

"1000";

end

Behavioral;

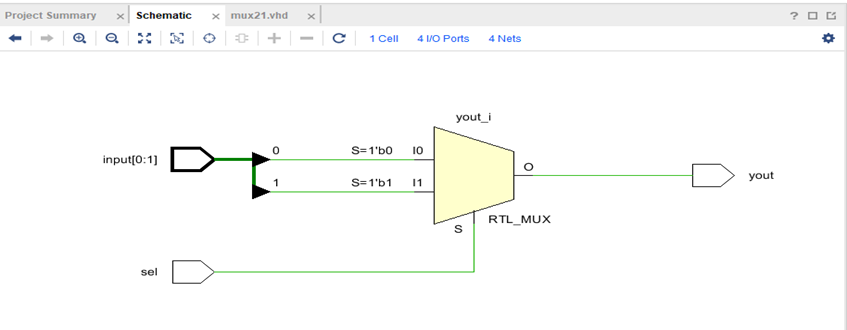

RTL Schematics for 2 to 4 Decoder

Simulation Waveform for 2 to 4 Decoder

VHDL Code for 3 to 8 Decoder

library

IEEE;

use

IEEE.STD_LOGIC_1164.ALL;

--

Uncomment the following library declaration if using

--

arithmetic functions with Signed or Unsigned values

--use

IEEE.NUMERIC_STD.ALL;

--

Uncomment the following library declaration if instantiating

--

any Xilinx primitives in this code.

--library

UNISIM;

--use

UNISIM.VComponents.all;

entity

dec3to8 is

Port

( w : in STD_LOGIC_VECTOR (2 downto 0);

EN

: in STD_LOGIC;

Y

: out STD_LOGIC_VECTOR (7 downto 0));

end

dec3to8;

architecture

Behavioral of dec3to8 is

component

dec2to4 is

Port

( enable : in STD_LOGIC;

sw

: in STD_LOGIC_VECTOR (1 downto 0);

led

: out STD_LOGIC_VECTOR(3 downto 0));

end

component;

signal

m0: STD_LOGIC;

signal

m1: STD_LOGIC;

begin

U1:

dec2to4 Port map(m1,w(1 downto 0),Y(7 downto 4));

U2:

dec2to4 Port map(m0,w(1 downto 0),Y(3 downto 0));

m0

<= NOT w(2) AND EN;

m1

<= w(2) AND EN;

end

Behavioral;

RTL Schematics for 3 to 8 Decoder

Simulation Waveform for 3 to 8 Decoder

Verilog

Program for 2 to 4 Decoder

//2 to 4 Decoder code

module decoder2to4(Y, A, E);

input [1:0] A;

input E;

output [3:0] Y;

reg [3:0] Y;

always @(E or A)

begin

if (E)

begin

if (A == 2'b00)

Y= 4'b0001;

else if (A == 2'b01)

Y = 4'b0010;

else if (A == 2'b10)

Y = 4'b0100;

else if (A == 2'b11)

Y = 4'b1000;

else

Y = 4'b0000;

end

end

endmodule

RTL Schematic for 2 to 4 Decoder

Verilog code for 3 to 8 Decoder

module decoder3to8(X,Y,A);

inout [2:0]A;

output[7:0]Y;

output [7:0]X;

wire s;

decoder2to4 x1(A[1:0],A[2],X[7:4]);

not(s,A[2]);

decoder2to4 x2(A[1:0],s,X[3:0]);

assign Y=s ?{4'b0,X[3:0]}

:{X[7:4],4'b0};

endmodule

RTL Schematic for

3 to 8 Decoder

Simulation Waveform for 3 to

8 Decoder

Result

Comments

Post a Comment